# **Retiming Of Fixed Point Digital Filter for Critical Path Reduction**

Mohd. Shizan Sheikh<sup>1</sup>, Prof. M.T. Hasan<sup>2</sup>

<sup>1</sup>(Department Of Electronics & Communication Engineering Anjuman College Of Engineering & Technology, Rashtrasant Tukadoji Maharaj Nagpur University, Nagpur, India) <sup>2</sup>(Department Of Electronics & Communication Engineering Anjuman College Of Engineering & Technology, Rashtrasant Tukadoji Maharaj, , Nagpur, India) Corresponding Author: Mohd. Shizan Sheikh

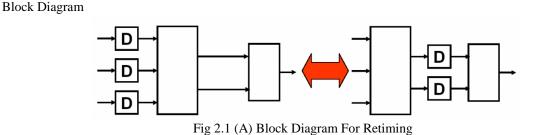

Abstract: This Work Describes A Circuit Transformation Technique Called Retiming In Which Registers And Added At Some Points In A Circuit And Removed From Others In Such A Way That The Functional Behavior Of The Circuit As A Whole Is Preserved. We Show That Retiming Can Be Used To Transform A Given Synchronous Circuit Into A More Efficient Circuit Under A Variety Of Different Cost Criteria. We Model A Circuit As A Graph In Which The Vertex Set V Is A Collection Of Combinational Logic Elements And The Edge Set E Is The Set Of Interconnections Each Of Which May Pass Through Zero Or More Registers. We Employ Retiming To A Fixed Point Digital Filter To Reduce The Critical Path Delay.

**Keywords** – Retiming, Fir Filter, Forward Retiming, Backward Retiming, Feed Forward Cutest Retiming \_\_\_\_\_

Date of Submission: 20-05-2018

Date of acceptance: 02-06-2018

\_\_\_\_\_

#### I. Introduction

Retiming Is The Technique Of Moving The Structural Location Of Latches Or Registers In A Digital Circuit To Improve Its Performance, Area, And/Or Power Characteristics In Such A Way That Preserves Its Functional Behavior At Its Outputs. The Technique Uses A Directed Graph Where The Vertices Represent Asynchronous Combinational Blocks And The Directed Edges Represent A Series Of Registers Or Latches (The Number Of Registers Or Latches Can Be Zero). Each Vertex Has A Value Corresponding To The Delay Through The Combinational Circuit It Represents. After Doing This, One Can Attempt To Optimize The Circuit By Pushing Registers From Output To Input And Vice Versa - Much Like Bubble Pushing. Two Operations Can Be Used - Deleting A Register From Each Input Of A Vertex While Adding A Register To All Outputs, And Conversely Adding A Register To Each Input Of Vertex And Deleting A Register From All Outputs. In All Cases, If The Rules Are Followed, The Circuit Will Have The Same Functional Behavior As It Did Before Retiming.

Retiming Is A Powerful Design Optimization Technique. However, Retiming Algorithms Have A Large Cost That Limits Their Use: The Efficient Retiming Of Large Circuits Remains Computationally Very Demanding, Even Though Sophisticated Optimization Techniques Have Been Introduced. Register Retiming Is A Circuit Optimization Technique That Moves Registers Forward Or Backward Across Combinational Elements In A Circuit. The Aim Of This Procedure Is To Shorten The Clock Cycle Or Reduce Circuit Area.

Retiming Is A Technique For Optimizing Sequential Circuits. It Is A Procedure That Repositions The Registers In A Circuit Leaving The Combinational Portion Unchanged.

The Main Objective Of One Form Of Retiming Is To Find A Circuit With The Minimum Number Of Registers For A Specified Clock Period.

To Reduce The Critical Path Using Retiming Of The Digital Circuit. 1.

To Changing The Position Of Existing Delay Elements. 2.

To Improve Circuit Performance By Optimizing Combinational Delay. 3.

#### **II.** Methodology

Retiming Means Changing The Position Of Existing Delay Elements. Retiming Improves Circuit Performance By Optimizing Combinational Delay. Difference Between Retiming And Pipelining Is Retiming Does Not Change The Input/Output Behavior Of The System.

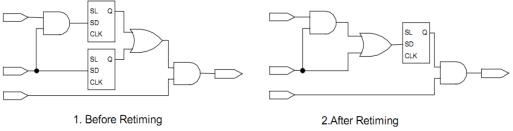

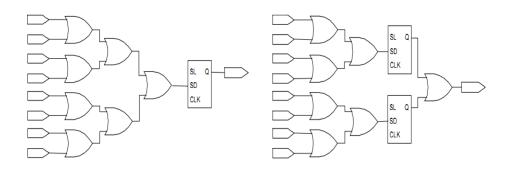

Basics Of Register Retiming: There Are Two Basic Types Of Register Retiming: Forward Retiming And Backward Retiming. Forward Retiming Refers To Removing A Fixed Number Of Registers From Each Input Or A Gate And Inserting The Same Number Of Registers At The Output. Conversely, In Backward Retiming We Remove A Fixed Number Of Registers From The Output Of A Gate And Insert The Same Number Of Registers In Front Of Each Input. Let Us First Consider An Example Of Forward Retiming In A Circuit With Simple Edge- Triggered Flip-Flops. In The First Part Each Input Of The Or Gate Is Driven By A Q- Pin Of A Register. Furthermore, Both Of These Registers Have Identical Clock Signals. Therefore, It Is Possible To Remove One Registers In The Original Version Became One Register In The Retimed Version; Therefore, The New Circuit Has A Smaller Area. Even More Importantly, If We Re-Synthesize The Logic Of The Retimed Circuit, It Is Possible To Eliminate The First Two Gates, Thereby Making The Circuit Even Smaller.

Fig 2.2(A) Forward Retiming.

Conversely, In Backward Retiming, A Register Is Deleted From All The Direct Fanouts Of A Gate And A New Register Is Inserted In Front Of Every Input Of The Gate. Figure 3.2 Illustrates This Concept And Also Shows How Retiming Can Be Used To Shorten The Clock Cycle. Notice That Before Retiming, The Critical Path Of The Circuit In Went Through Three Gates, Whereas After Retiming, This Path Has Been Shortened To Two Gates. This Allows Us To Increase The Clock Speed.

Before Retiming Fig 2.2(B) Backward Retiming

After Retiming

## III. Data Flow Graphs

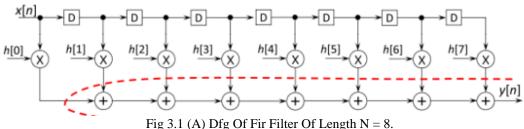

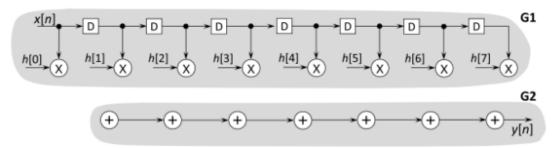

Fig 3.1 (B) Decomposition Of Dfg To Two Subgraphs G1 And G2 For Feed-Forward Cutset Retiming Of Dfg.

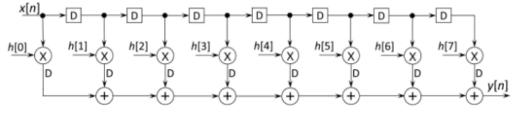

Fig. 3.2(A) Retimed Dfg.

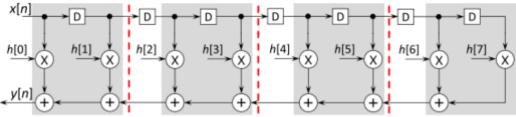

Flexible Retiming Of Fir Filter Based On Connected Component Timing Model: We Discuss Here A Flexible Scheme For The Retiming Of The Dfg Of Fig. 3.1(A). To Perform The Desired Retiming The Direction Of Accumulation Path In The Dfg Is Reversed [As Shown In Fig. 3.1(A)], And The Cutsets Across The Dashed Lines (After Each Gray Box) Are Considered One After The Other For Retiming.

Fig.3.3(A) Cutset Selection For The Proposed Retiming Of Dfg Of The Fir Filter Of Length N = 8.

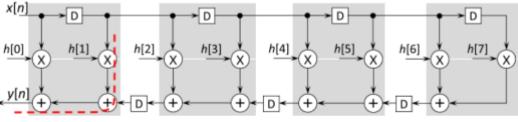

Fig.3.3(B) Retimed Dfg.

# **IV. Conclusion**

The Proposed Techniques Can Be Helpful For Less Pipeline Overheads As Exact Estimation Of Propagation Delays Can Be Made By Connected Component Model, Which Results Easy Way To Obtain Exact Estimation Of Propagation Delays Over Different Paths In Dfg. The Advantage Of Proposed Retiming Technique Is Critical Path Reduction, Later It Shown That The Splitting And Merging Of Nodes May Results Less Combination Path Delays. This Techniques Of Fixed Point Circuits Can Be Extended To Floating Point Circuits. These Methods Could Be Useful In Digital Signal Processing And Fir, Iir Filters.

## V. Future Scope

Currently, The Cost Model Only Considers The Hardware Cost Of Arithmetic Components, Other Components, E.G. Memories, Interfaces, Were Assumed Occupying Insignificant Resources. A More Accurate Model Can Be Developed, Which Will Take These Factors Into Account. Moreover, Timing Constraint Can Also Be Considered, E.G. Logic Delay, Clock Cycles Can Be Added Into The Cost. A More Robust Error Reporting Mechanism Can Be Used. For Example, Each Object Can Be Associated With A Flag, Which Can Indicate Arithmetic Error, Such As Overflow And Underflow, Occurred During Simulation.

#### References

- [1]. Deepa Yagain,"Fir Filter Design Based On Retiming & Automation Using Vlsi Design Metrics" 2013 International Conference On Technology, Informatics, Management, Engineering & Environment (Time-E 2013) Bandung, Indonesia, June 23-26,2013.

- [2]. Vishal Awasthi," Design Of Efficient Digital Filter Using Cutset Retiming Technique" Ijeecs Issn 2348-117x Volume 2, Issuel January 2014.

- Pramod Kumar Meher," On Efficient Retiming Of Fixed-Point Circuits" Ieee Transactions On Very Large Scale Integration (VIsi) [3]. Systems 2016.

- [4]. Y.Diao And Y. L. Wu "A Fast Retiming Algorithm Integrated With Rewiring For Flip-Flop Reductions", 2011 12th International Conference On Computer-Aided Design And Computer Graphics 2011.

- [5].

- Karolína Netolická, "*Equivalence Checking Of Retimed Circuits*", *Massachusetts Institute Of Technology* June 2005. Sam Farrokhi, Masoud Zamani, Hossein Pedram, Mehdi Sedighi "Asynchronous Behavior Related Retiming In Gated-Clock Gals [6]. Systems", Ieee Ewdts, Yerevan, September 7-10, 2007.

- P. Y. Calland, A. Mignotte, O. Peyran, Y. Robert, And F. Vivien,"Retiming Dag's", Ieee Transactions On Computer-Aided Design [7]. Of Integrated Circuits And Systems, Vol. 17, No. 12, December 1998.

- Soha Hassoun And Carl Ebeling. "Architectural Retiming: Pipelining Latency-Constrained Circuits" 1996 Acm. [8].

- [9].

- Josi Monteiro, Srinivas Devadas Abhijit Ghosh, "*Retiming Sequential Circuits For Low Power*", *Ieee* 1993 . Xun Liu, Papaefthymiou, Eby G. Friedman, "*Retiming And Clock Scheduling For Digital Circuit Optimization*", *Ieee, Ieee* [10]. Transactions On Computer-Aided Design Of Integrated Circuits And Systems, Vol. 21, No. 2, February 2002.

Mohd. Shizan Sheikh "Retiming Of Fixed Point Digital Filter for Critical Path Reduction "International Journal of Engineering Science Invention (IJESI), vol. 07, no. 05, 2018, pp 68-71 \_\_\_\_\_